|

|

x Ne-Seiten

|

>FET b< 22.06.2006 (19.08.2009) # 15

|

|

|

>FET b<

|

|

Beschreibung der Arbeitsweise der Power FET’s

|

|

die rechts auf der Seite dargestellten Skizzen / Blockschaltbilder finden Sie am Ende dieser Seite noch einmal.

|

|

D i e P O W E R F E T s

|

|

AP 5) So löse ich die Ansteuer- und Kühlprobleme.

5 A)In meinen Schaltung bevorzuge ich eine steile Einschaltung des Motorstromes von 2...7usec. Deshalb ist die Treiberstufe mit einem Transistor „T78“ ausgeführt, oder mit einem MOS-FET-Treiber. So werden die Ladezeit der Gatekapazitäten sehr gering, da der Arbeitswiderstand einen kleinen dynamischen Widerstandswert von ca. 100r hat. Wird der Impuls auf 0V getaktet (Strom aus) muß hier nur ein geringer Strom , der Basisstrom über einen 27k Widerstand geschaltet werden.

Würde / wird die Spannung über einen reellen Widerstand von 1k zugeführt, wie es in einfachen Schaltung ausgeführt wird, ist die Ladezeit lang, der Impulsanstieg auch entsprechend langsam.

Heute werden oft MOS-FET Treiber eingesetzt, die noch niederohmiger, noch steiler ansteuern. Die MOS-FET Treiber TC4427 / MIC 4427 vertragen eine max. Akkuspannung von 20V. Bei 20,7V gehen sie defekt. Spezielle Schaltungsvarianten müssen bei hohen Fahrakkuspannungen die Spannung entsprechend begrenzen. Auch vor Impulsspannungen größer 20,7V ist der MOS-FET Treiber zu schützen, deshalb R33 (220r) in die +Zuführung zum MOS-FET Treiber mit einem C33 (1uF) nach Masse. Mit T84 wird die hohe Spannung des Fakrakkus auf 18V begrenzt. Derzeit keine Skizze

Diese steilen / schnellen Stromeinschaltungen führen manchmal auch zu Störproblemen, sodaß es vorkommt, daß spezielle bei dem MOS-FET Treiber ein Widerstand (100 bis 220r) in die gemeinsame Gatezuleitung eingebaut werden muß. Die Forderung nach einzelnen Gatewiderständen bleibt trotzdem bestehen. Dies liegt an den Induktivitätsanteilen der Akku-Zuleitung und der Akkus selbst.

5 B)Für die Motorstromimpulsausschaltung wären steile Impulsabfallflanken (1...5usec) in Bezug auf die geringere Wärmeentwicklung von Vorteil.

FET S. 3e/..

Seite FET S. 3f

Was mit T77 ohne R77 (D77 ohne R77), oder einem MOS-FET Treiber realisieren läßt. Dies würde aber zu riesigen Induktionsspitzen / Induktionsleistung (an der Motor-Induktivität) führen. Diese Induktionsspannungen müssen entweder:

5B1) mit den Freilaufdioden (D5, D6...) zum +Fahrakku abgeleitet werden, die Endstufe bleibt jetzt kälter, die Freilaufdioden erhitzen sich mehr bei einer schnellen Motorstromimpulsabschaltung.

5B2) oder die Induktionsspannungen vernichten sich selbst, indem die Spannungsspitzen über die Zenerdiode-, Diodeneinheit zum Gate des FETs zurückgekoppelt werden und diesen für einen gewissen Zeitraum (während des Bestandes der Induktionsspitzen) noch leicht leitend gehalten werden. Wird die gesamte Induktionsleistung auf diese Art vernichtet, wird die Endstufe riesig warm, man kann allerdings

5B3) die heutigen Power - FETs haben meist eine Evelanchdiode, die Drain - Source Spannung auf eine gewisse Spannung begrenzt. Hier wird die Spannung über eine „Zenerdiodenstrecke“ im FET abgeleitet. Auch dies garantiert eine sehr starke Erwärmung der FETs durch die Induktionsspannungen, bei fehlender Freilaufdiode, oder Steiler Abschaltungstakte.

5B4)Eine extrem langsame Abschaltung (100usec....300usec) vermeidet Induktionsspannungen. Durch die lange Stromabschaltzeit ergibt sich aber auch eine kräftige Erwärmung der FETs und ist bei den gewünschten Taktfrequenzen von 1...5kHz nicht realisierbar.

FAZIT) Aus den aufgezeigten Problemen heraus, bevorzugen meine Schal-

tungen eine steile Motorstrom Einschaltung von 2...5usec. wie unter AP 5a). Die Abschaltzeiten liegen bei 10...30usec. So wird die Verlustleistung, die in Wärme umgesetzt wird, auf die FETs und die Freilaufdiode verteilt. Die Freilaufdiode leitet die Induktionsspannungen zum Fahrakku. Ein Elko 5uF...10uF oder gar 220uF ist

eine weitere Optimierung in Bezug auf Induktionsspannungsverlauf, Störung usw.. Wobei dieser Elko „C35“ nicht so groß sein darf, da er sich durch den Spannungshub des Fahrakkus, zwischen dem Fahrstromimpuls und der Strompause, erwärmt (Umladestrom).

|

|

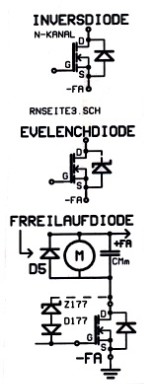

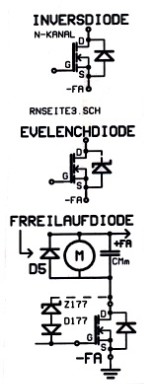

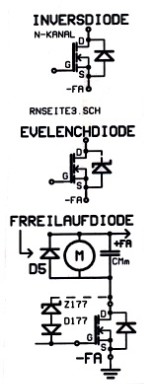

AP 6) INVERSDIODE Jeder Power FET hat die Inversdiode von Drain nach Source automatisch dabei. Sie schaltet bei einem N-KANAL-FET eine eventuelle am Drain negativ eingespeiste Spannung direkt zur Source durch. Dies kann man nicht verhindern. Sie wirkt wie ein Diode.

Beim P-KANAL FET liegt die Anode am Drain und schaltet positive Spannungen zur Source.

EVELENCHDIODE Die im Modellbaubereich eingesetzten Power FETs der 20V, 30V, 50V, 60V und 80V Klasse haben anstelle der Inversdiode diese als EVELENCHDIODE ausgebildet. Diese Evelenchdiode arbeitet auf der Innenseite wie die Inversdiode. Überschreitet die Induktions-Spannung die Evelenchspannung, so wird diese Überspannung über die Zenerdiodenstrecke der Evelenchdiode abgeleitet / vernichtet. Erfolgt dies mit der Taktfrequenz des Motorstromes, erhitzt sich der FET schnell und kräftig.

FREILAUFDIODE Wie in den Kapitel 5b) und bei „FAZIT“ bereits erwähnt, sollen die Freilaufdioden die Induktionsspannungen zum Fahrakku ableiten. Diese Dioden sollen schnell sein und einen kleinen Spannungsabfall an der Anoden - Katodenstrecke haben, um ihre Erwärmung gering zu halten. Superschnell müssen diese Freilaufdioden nicht sein, da wir ja eine begrenzte Impulsflankensteilheit sowohl beim Strom- Ein- als auch beim Aus-Takten haben. Hier werden bevorzugt 3A, 5A (axiale), 5A, 10A, 16A Dioden im TO220 eingesetzt. Zum Einen Schottky Dioden, oder Epitaxial Dioden (schnell). Die Anzahl der Freilaufdioden richtet sich nach dem Motorstrom. Bei 50A z. B. 2...3 3A Typen BYV28-100, SB360 (Schottky). Bei 100A bis 200A 5 SB560 (5A) oder Typen im TO220.

AP 7) Der Strom eines FETs.

Eine Faustregel sagt zunächst einmal aus, daß wir im Modellbaubereich, bei den Minuten-Dauerströmen eine Restspannung von 0,2V an einem FET zulassen, um keine zu große Erwärmung in den Minuten des Stromflußes zu erzielen. Bei den heute sehr niederohmigen FETs SUP75N03-04 (ein 30V Typ, Logic level mit 4 mr RDSON ) würde ich aufgrund des nur TO220 Gehäuses keine 50A in die Dauerstromrechung für die Endstufe einbringen, sondern nur 20A bis max. 25A, bei SMP60N03-10L (30V, LL - Typ, 10mr) / IRL2203 (30V, LL - Typ, 7mr) nur 10A...15A. Das andere halte ich mir als stille Reserve. Mit einer gespeicherten Spannung für die Gateansteuerung (in C75) ergibt dies robuste Endstufen, auch in einer Unglückssituation, wo die Fahrakkuspannung kurzzeitig zusammen bricht.

Das oben gesagte bezieht sich auf Power - FETs im TO220 / TO263 Gehäuse ohne extra Kühlung. Jetzt kommen die SMD Gehäuseformen hinzu, die eine kleinere Wärmekapazität haben. Hier würde ich für die zuvor ausgeführte Rechnung eine Restspannung von nur 0,1V pro FET zugrunde legen.

Power - FETs im „little foot“ oder SO8 Gehäuse haben ja fast keine Wärmeableitfläche. Hier sollte man bei standartmäßigem Einsatz (ohne extra Kühlflächen auf der Auflötfläche) von 1 bis max. 2A pro FET ausgehen.

FET S. 3 F /.........

.

|

|

FET Seite 3g

AP 9) Der Einschaltwiderstand DRSon am Beispiel des BUZ11.

Der BUZ11 / BUZ11S2 - der SIPMOS-POWER-FET von Siemens entwickelt, seit ca. 1986 auf dem Markt - wird heute von fast allen namhaften Halbleiter-Herstellern mit den von Siemens bekanntgegebenen Daten geliefert. Die Evelenchdiode die im Siemens BUZ11 ist, haben heute fast alle Hersteller bei den Power - FETs integriert. Der BUZ 11 hat nach dem Datenblatt einen RDSon von 40mr = 0,040r = 0,04W bei 12V UGS Die reellen Einschaltwiderstände liegen bei den Siemens-Typen seit jeher besser. Deshalb gebe ich in meinem Prospekt oft die aktuellen RDSon Werte an, von den Typen, die am Lager sind. Der BUZ11 ist heute (1998) nicht mehr der primäre FET - Typ der im Modellbaubereich zum Einsatz kommt, aber aus historischen Gründen möchte ich einmal beim BUZ11 (Siemens) bleiben, der über lange Jahre der Typ war.

Wird die Gatespannung UGS von 12V auf 20V erhöht, so verbessert sich der RDSon um ca. 15...20%, was für alle FETs gleichermaßen gilt.

Da sich die Daten der Power - FETs mit höherer Gatespannung verbessern, so ist dies ein Grund für den Einbau von Spannungsdopplern „SDS“ und Verdreifacherstufen. Diese „SDS“ Stufen bleiben auch bei den Logic level FETs „LL - Typ“ im Betrieb. Durch den Einsatz der Spannungsdoppler werden die Power – FET - Endstufen bei einem Kurzschluß unempfindlicher.

AP 9a) Messen der angegebenen Daten: Einschaltwiderstand RDSon .

Ich vermesse meine Power - FETs mit einem Dauerstrom von 5A / 10A, wobei der Power -FET auf einem Kühlkörper montiert ist. Somit kann er sich nicht wesentlich erwärmen und die gewonnenen Daten sind immer wieder vergleichbar, während die Gatespannung verändert wird.

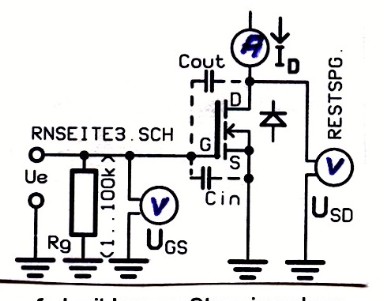

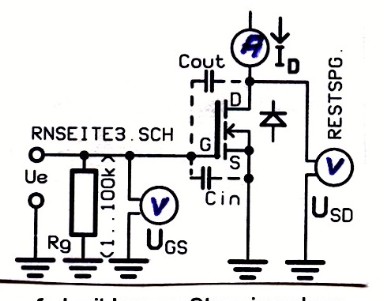

Abb. ist unten AP 9a) FET-3f-a

Damit der Power - FET nicht gelötet werden muß, stecke ich eine Buchsenleiste auf die 3 Elektroden und messe mit den Meßspitzen des Voltmeters direkt an den Elektroden Drain „D“ und Source „S“ hinter dem Plastikaustritt die Restspannung.

Bei den Herstellern werden die Daten des Einschaltwiderstandes für den Strompfad mit kurzen Stromimpulsen (einige µsec) vermessen. So erwärmen sich die Power - FETs beim Testen auch nicht, denn die Angaben sind normalerweise auf 20 Grad bezogen. Andere Kollegen ermitteln die Temperatur, auf die sich der Power - FET bei einem gewissen Strom, in einen konstanten Zeit erwärmt. Auch so werden Qualitätsunterschiede ermittelt.

|

|

AP 10) POWER FETs und LOGIK LEVEL FETs „LL“-Typen.

Allgemein öffnen die FETs bei einer Gatespannung von 5V den Stromkanal und sind bei 6V gut angesteuert. Die Daten des RDSon in den Datenblättern sind für eine Gatespannung U GS von 12V garantiert, auch bei den „LL“ FETs. Die meisten FETs der Normalklasse erreichen aber den Wert des RDSon des Datenblattes bereits bei einer Gatespannung von 7.....8V, die Logic level Typen bei 5,5V bis 6V.

Bei den Philips Semiconductors / Hitachi, die „Trench FETs“, sind Gate - Spannungen von 15V und 20V meist nicht zulässig, da diese FET Typen oft eine Gatespannungsbegrenzung auf ±12V im Gateeingang haben. Sie belasten damit die Treiberstufen und der „Trench FET“ wird ggf. durch einen Gate - Strom warm.

AP 10a) Die Logic Level FETs

öffnen den Stromkanal bereits bei 3,0 bis ca. 3,5V und liegen bei 4V schon gut in der Stromführung. Siehe anschließender Widerstands-Datenvergleich. Diese „LL“ - FETs sind unter anderem für die direkte Ansteuerung aus 5V ICs (MOS - ICs, Mikroprozessoren usw.) angedacht. Aber eine Gatespannung von 18V schadet ihnen auch nicht, Ausnahme die „Trench - FETs“ (Hitachi, begrenzen die Gatespannung ).

Bei den FET - Chargen gibt es immer Unterschiede im RDSon Daten. Die hier ausgewählten FETs sind zufällig gewählt, in der nächsten Charge können die Daten besser, aber auch schlechter sein.

|

|

AP 10b) Widerstandsdaten RDSon in Abhängigkeit der Gatespannung

so wie die hier ausgewählten FETs, verhalten sich alle, mit steigender Gatespannung sinkt der Widerstand des Stromkanals. Bei 28 V zerplatzen die meisten FETs.

|

|

Typ

|

IRFZ

46N

|

SMP60N0 6-18

|

SUP75N06 -08

|

IRL3205

|

SMP60N03 -10L

|

IRL2203N

|

IRL3803

|

SUP75N03- 04

|

|

|

3,0 V

|

zu

|

zu

|

zu

|

zu

|

öffnet

|

öffnet

|

zu

|

öffnet

|

|

|

3,5V

|

zu

|

zu

|

zu

|

zu

|

öffnet

|

öffnet

|

zu

|

öffnet

|

|

|

4,0 V

|

öffnet

|

zu

|

600 r

|

850 r

|

700 r

|

ca. 9 r

|

ca. 7 r

|

ca. 4 r

|

|

|

4,5 V

|

990 r

|

340 r

|

ca. 7 r

|

??

|

250 r

|

___

|

___

|

_____

|

|

|

5,0 V

|

37 r

|

39 r

|

11 r

|

12 r

|

ca. 12 r

|

ca. 7 r

|

ca. 5,7 r

|

3,2/3,7r

|

|

|

6,0 V

|

24 r

|

17 r

|

8,4 r

|

8,4 r

|

8,8 r

|

6,4 r

|

5,1 r

|

3,0/3,2 r

|

|

|

7,0 V

|

15 r

|

15,6 r

|

7,4 r

|

7,5 r

|

7,7 r

|

6,0 r

|

4,6/ 4,7 r

|

2,6 /2,8r

|

|

|

10,0 V

|

17,4 r

|

12,0 r

|

6,4 r

|

6,5 r

|

6,6/7,2 r

|

5,4/5,4 r

|

4,2/4,3 r

|

2,4/2,8 r

|

|

|

15,0 V

|

15,4 r

|

12,0 r

|

6,4 r

|

5,6 r

|

6,4/6,8 r

|

5,0/5,0 r

|

3,9/3,9 r

|

2,4/2,7 r

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FET S. 3 H /..........

FET Seite 3i

AP 12) N i c h t s e l b s t l e i t e n d e F E T s = POWER-FETs und Selbstleitende F E T s

Die Power - FETs im Modellbau-Einsatz sind alles Nicht-Selbstleitende Typen = ENHENCEMENT Typen = Anreicherungstyp. Beispiel: Ist ein Gatewiderstand zur Source = Masse (für einen N-Kanal FET) von z. B. 100kW eingebaut, so muß eine Spannung an das Gate angelegt werden, um einen Stromfluß zu bewirken. Ohne einen Gatewiderstand in diesem Beispiel, könnte eine + Ladung am Gate sein, die den FET öffnet.

Selbstleitende Typen = JUNCTION FETs sind für Laststromaufgaben nur wenige auf dem Markt (ND2406). In der Verstärkertechnik sind diese Typen (früher) eingesetzt worden (2N3819, BF246, TIS59, U232 (P), 2N3822 usw., für 10mA bis 100mA). Hat dieser Selbstleitende Typ einen 100k Gatewiderstand nach Source, so ist der Stromkanal geöffnet. Erst mit einer „-“ Sperrspannung am Gate wird der Strom unterbunden. Siehe Charakteristik / Kennlinien S. 3 h.

|

|

Zu AP 13) FET-3g-a Abb.: FET-3e-a.jpg

|

|

AP 13) Die Arbeitsweise der FETs,

Hier der SIPMOS-FET (Siemens, Chiprand-Querschnitt S. 3h)

basiert auf der Wirkung des elektrischen Feldes in einem Halbleitermaterial. Das elektrische Feld öffnet oder schließt einen Stromkanal von der Source (Quelle) zum Drain (Sammler). Es ähnelt einer Elektronenröhre, die auch mit einem Elektronenfluß im mA-Bereich arbeitet. Ein FET yerarbeitet jedoch ohne Heizung und bereits mit kleinen Spannungen an der Steuerelektrode „GATE“ ab 3V und Strömen von 1mA bis 10A ja 100A, bei fast 0V.

In der Abb. 1a) ist das Ersatzschaltbild der N-Kanal Power - FETs dargestellt und Kennlinienfelder des BUZ11 (Siemens). In der Abb. 2a) bis Abb. 2c) ist dann im Schaltbild die Elektronenverteilung auf den Elektroden des FETs im geschlossenen und leitenden Zustand dargestellt.

Über die immer vorhandene Inversdiode kann der FET - Typ ermittelt werden, die Inversdiode schließt die Spannung mit der falschen Anschlußrichtung kurz. Die Inversdiode ist heute meist als Evelenchdiode ausgelegt, sodaß die Überspannungen = Induktionsspannungen vernichtet werden, siehe hierzu AP 6).

Abb. 2a: Zwischen dem Gate „G“ (Steuerelektrode, Gitter), der Source „S“ (Quelle) ist keine Spannung UGSangelegt. Trotz der angelegten Spannung am Drain „D“ (Sammler) UDS ist der FET stromlos. Dies bewirkt die isolierende Wirkung der ladungsträgerarmen P-Schicht.

Abb. 2b: Das Gate hat jetzt eine positive Spannung UGS gegenüber der Source, die über der Schwellspannung liegt. So fließen zunächst negative Ladungsträger in die ladungsträgerarme P-Schicht (Kondensatorladestrom). Somit werden Source und Drain elektrisch miteinander verbunden. Der Stromfluß kann in beiden Richtungen erfolgen, ohne eine Schwellspannung zwischen Source und Gate überwinden zu müssen. So könne die FETs mit dem Einschaltwiderstand RDSon definiert werden.

Ein Power - FET besteht aus vielen parallelen Zellen, ca. 1.000 pro qmm, in den neuen FETs z. B. SUP75N06-08 ca. 010.000 Z./ qmm.

Abb. 2c: In dieser Abb. ist der Stromfluß in vollem Gang, ohne daß ein Gatestrom fließt. Da die FETs unipolar sind, sind die Einschaltzeiten kleiner 0,1usec, ebenso die Ausschaltzeiten. sind Induktivitäten im Stromkreis geschaltet, so ergeben sich hohe Spannungsspitzen beim Ein- und Ausschalten des Stromes. Spezielle auf die Abschalt-Spannungsspitzen = „Induktionsspannungen“ muß geachtet werden, siehe AP 6).

Unipolar:nur die Elektronen sind für den Stromfluß in den FETs zuständig und die sind schnell beweglich. Es gibt nur geringste Ausräumzeiten für die P-Schicht.

Bipolar: Im Gegensatz zum FET ist der normale Transistor bipolar. Hier ist der Elektronenstrom und der Lochstrom für den Stromfluß zuständig. Der Lochstrom fließt / bewegt sich langsamer, sodaß der p-n-Übergang immer eine gewisse Zeit zum Ausräumen der Ladungsträger benötigt.

Kennlinienffelder ¯®

Ersatzschaltbild der FETs

|

|

AP 14) Gehäuseformen

Das TO 220 Gehäuse ist die häufigste Gehäuseform für die Power - FETs die im Modellbaubereich eingesetzt werden. Dieses Gehäuse wird auch isoliert geliefert. Der Power - FET wird dadurch etwas dicker und die mögliche Wärmeableitung wird vermindert. Die isolierende Schicht am Metallrücken läßt sich entfernen. Der ungekühlte Power - FET im TO 220 Gehäuse kann mit ca. 1W belastet werden, wird es gekühlt, können 20--30W Leistung, bei besonderer Montage auch mehr abgeführt werden.

Das TO 263 Gehäuse ist die SMD Variante des TO220 Gehäuse. Hier fehlt ein Teil der Metallasche und die Anschlußdrähte sind gekürzt und umgebogen für den SMD Einbau.

Das TO 251 Gehäuse ist nur 7mm breit. Diese FETs sind für kleinere Leistungen gedacht. Der Drahtabstand ist aber auch 2,5mm, wie beim TO 220.

TO 252 ist das SMD Gehäuse vom TO251. Anschlußdrähte sind gekürzt, für SMD Montage + abgekröpft.

T0 218, TO 247, TO 248 sind 15mm breite Gehäuse, die Wärme viel besser an einen Kühlkörper abführen können als das TO 220 Gehäuse. Hier schätze ich das TO 247 besonders.

SMD Abwandlungen sind hier nicht dargestellt.

LITTLE FOOT ist eine SMD Gehäuseform und ist so groß wie z. B. ein 8-poliges SMD-IC „LM393“, „LM358“, „NE555“. Ein aufgelöteter „Little Foot“ Power - FET darf mit 0,5...1W...2W ohne besondere Kühlung belastet werden, je nach der Wärmeleitfähigkeit (Dicke) der Kupferschicht.

|

|

AP 15) Temperaturkontrolle der Endstufe mit PTC.

In der Vergangenheit habe ich sehr selten Temperaturkontrollen in meinen Drehzahlstellern eingesetzt. Ein nachträglicher Einbau bereitet aber in meinen Drehzahlstellern keine Probleme, da ich überall eine Unterspannungskontrolle „FUS“ habe, die Endstufe bei einer Akkuunterspannung abschaltet. Für die Temperaturkontrolle eignet sich ein PTC, von denen auch 2...5 in seriegeschaltet eingebaut werden können, um verschiedene Bereiche zu kontrollieren.

Der PTC ist in seinem Arbeitsbereich niederohmig, er hat einige hundert W, wird die Abschalttemperatur erreicht, wird er hochohmig. Dies ist reversibel, d. h. er schaltet immer an seinem Umschaltpunkt von Niederohmigkeit auf Hochohmigkeit um.

Der Einbau erfolgt wie gesagt in den „FUS“ Kreis, hier wird er bei „R41“, bzw. Bei R42 - R41 eingebaut. Siehe Schaltbeispiel in meinen Schaltungen und S. 18/19 der Anhangseiten.

|

|

AP 16) Legende zu den Parametern der technischen Daten einiger Power - FETs.

UDS. Dies ist die Spannung von Drain nach Source.

RDSon ist der Einschaltwiderstand des Stromkanals von Source nach Drain . Dieser Wert im Datenblatt ist allgemein ein garantierter Wert, bei einer Gatespannung von 12V.

„Typ.“ Hier sind gemessene Werte des RDSon eingetragen. Viele FETs erreichen den garantierten RDSon bereits bei einer Gatespannung von 6....7V.

mit/ohne Evelenchdiode heißt, daß die Inversdiode bei den Typen „mit“, als Zenerdiode von Drain nach Source ausgebildet ist. Der FET ist „evelenchfest“, „evelench proof“.

UGS Alle seitherigen N-Kanal und P-Kanal Power - FETs vertragen ein Gatespannung von ±20V. Oberhalb von 27V gehen sie defekt. Neu: Die 10mW und andere Trench-FETs (Philips) haben ene Begrenzungszenerdiode im Gate von 12V. Hitachi hat ebenfalls solche Typen UGS GRENZ ?

Cin ist die Eingangskapazität, der für die rechnerische Auslegung der Treiberstufe wichtig ist, damit die Ein-, Ausschaltimpulse die richtige Steilheit haben.

Cout ist die Ausgangskapazität, die ebenfalls für die rechnerische Auslegung der Treiberstufe wichtig ist. Sie wirkt von der Source zum Gate.

ID / Id ist der Dauer- und Impulsstrom lt. Datenblatt, bei 20 oder 25Grad. AP4), AP5).

Min. Dauer Der Minuten-Dauerstrom ist der Dauerstrom für 1 FET dieses Typs, ungekühlt, für die Dauer der Stromabgabe des 1,4Ah Akkus. Dieser Wert spiegelt sich die Restspg. von 0,2V wieder

Zgs Zenerdiode im Gate - Eingangskreis, bei Hitachi ±20V, bei Philips „Trench - FET“ ±12V

X diese sind im Programm w FETs waren im Programm n neuer Typ, der kommt.

|

|

Legende dieser F E T - Beschreibung.

1. Teil der FET Beschreibung

S. 3 AP 1) Gefahr für FETs

AP 2) FET Durchbruch EVELENCHFEST

S. 3a: AP 3a) Widerstandstest des FETs

AP 3b) Überprüfung der FETs, ob sie noch arbeiten, im ausgebauten Zustand.

S. 3b AP 3) Fehlersuche in der defekten FET -Stufe

AP 3d) FET Brücke, Halbbrücke

S. 3c: AP 3e) Arbeiten alle FETs in der Gruppe?

2. Teil der FET Beschreibung

S. 3c AP 4) Was kann ein FET ungekühlt vertragen.

S. 3d AP 4b) Einschaltwiderstand des FET.

: R DSON bei Temperatur und Gatespannung

AP 5) So löse ich Ansteuer- und Kühlprobleme der Endstufe

S. 3e: AP 6) Induktionsspannungen (Inversdiode, Evelenchdiode, Freilaufdiode

AP 7) Der Strom eines FETs

S. 3f: AP 9) Der Einschaltwiderstandes R DSON am Beispiel des BUZ11 (Siemens)

AP 10) Logik Level FETs, RDSON Vergleich beliebter FETs.

S. 3g: AP 12) Nichtselbstleitende-, selbstleitende FETs

AP 13) Arbeitsweise der SIPMOS FETs (Siemens)

S. 3h: AP 13b) es folgt noch Arbeitsweise „HEXFET“, TRENCH-FET..(Chamtischer Aufbau)

S. 3i AP 11) Schaltungsbeispiele demnächst

S. 3k AP 14) Gehäuseform demnächst

AP 15) Temp. Kontrolle (auch S. 3d, AP 4a),

AP 16) Legende der Parameter, N-, P- FETs

|

|

AP 9a) FET-3f-a AP 9a) FET-3f-a

|

|

|

|

|

AP 9a) FET-3f-a

AP 9a) FET-3f-a